# Lecture 8 - 06/11/2024

#### The *p-n* junction

- Basic considerations

- At thermal equilibrium

- Space charge region

# **Summary Lecture 7**

#### Carrier mobility at low electric field

$$v_d = \mu_0 E$$

$\mu_0$  ... low field mobility

$$\frac{1}{\mu_0} = \frac{1}{\mu_{\rm LA}} + \frac{1}{\mu_{\rm LO}} + \frac{1}{\mu_{\rm ion}} + \cdots \text{ Matthiessen rule}$$

#### Out of equilibrium semiconductors

$pn \neq n_i^2$  due to excess carriers injected by electrical or optical means

$$\frac{\partial n}{\partial t} = G - R + \left(\frac{1}{e}\right) \nabla \cdot \mathbf{J_n}$$

$$\frac{\partial p}{\partial t} = G - R - \left(\frac{1}{e}\right) \nabla \cdot \mathbf{J_p}$$

$$\frac{\partial p}{\partial t} = G - R - \left(\frac{1}{e}\right) \nabla \cdot \mathbf{J_p}$$

$$processes to restore equilibrium (processes to restore equilibrium$$

#### Carrier mobility at high electric field

$$v_d = \mu_0 \, E \sqrt{\frac{T}{T_e}}$$

$T_e$  ... Carriers' effective temperature  $T$  ... Lattice (phonon) temperature

$$\frac{T_e}{T} = \frac{1}{2} \left[ 1 + \sqrt{1 + \frac{3\pi}{8} \left( \frac{\mu_0 E}{c_s} \right)} \right] \qquad c_s \dots \text{ velocity of sound}$$

$$v_s = \sqrt{\frac{8E_{ph}}{3\pi m^*}} \approx 10^7 \, \mathrm{cm/s}$$

$v_s \dots$  saturation velocity  $E_{ph} \dots$  optical-phonon energy

$$G = G_{th} + G_L$$

processes to restore equilibrium  $(pn = n_i^2)$ :

$$pn > n_i^2 \dots$$

recombination, rate  $R$

$$pn < n_i^2$$

... thermal generation, rate  $G_{th}$

# **Summary Lecture 7**

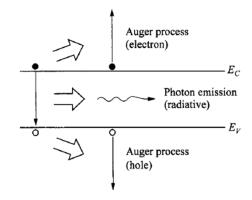

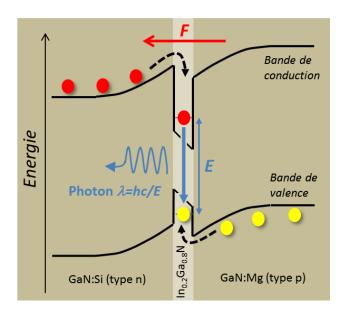

#### **Band-to-band recombination – photon emission**

Far more probable in direct-bandgap SCs weak to moderate injection ( $\leq 10^{18}~{\rm cm}^{-3}$ ):

$$R \,-\, G_{th} = egin{cases} 0 & ext{thermal equilibrium} \ rac{n-n_0}{ au_n} & ext{$p$-type} & ppprox p_0 \ \ rac{p-p_0}{ au_p} & ext{$n$-type} & npprox n_0 \end{cases}$$

#### **Band-to-band recombination – Auger-Meitner process**

At play in both direct- and indirect-bandgap SCs high injection (  $> 10^{18} \, \mathrm{cm}^{-3}$ ):

$$R_A - G_{th} \propto egin{cases} p^2 n & extit{p-type} & p pprox \Delta p \ n^2 p & extit{n-type} & n pprox \Delta n \end{cases}$$

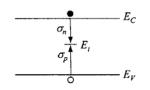

#### Single-level recombination - traps

Dominating at low injection in both direct- and indirect-bandgap SCs

- (1) electron capture from CB

- (2) electron emission to CB

- (3) hole capture from VB

- (4) hole emission to VB

$$\frac{dn}{dt} = G_L + R_n = G_L + r_{e,n} - r_{c,n}$$

$$R_n = r_{e,n} - r_{c,n} = v_{th}\sigma_n(nN_t^{\times} - n_tN_t^{-})$$

$$N_t^{\times} = N_t(1 - f), \quad N_t^{-} = N_t f$$

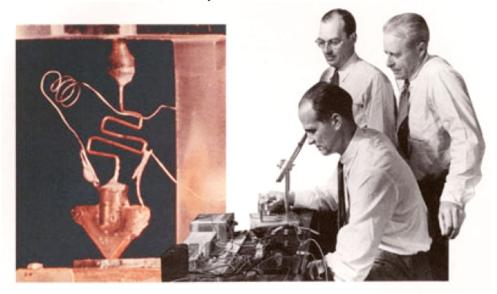

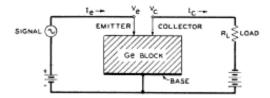

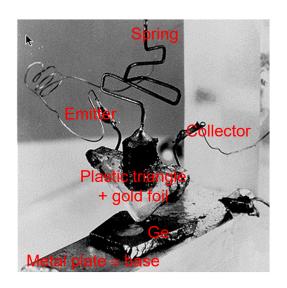

# 1<sup>st</sup> *p-n* junction and 1<sup>st</sup> transistor (1947)

First transistor Bardeen, Shockley and Brattain 1947

#### **Point contact transistor**

Fig. 1. Schematic of semi-conductor triode.

J. Bardeen and W. H. Brattain, Phys. Rev. **74**, 230 (1948) > 520 citations

**Nobel prize in physics 1956**

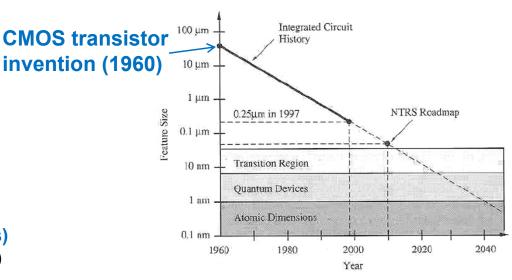

### Transistor: past... and ...future

First integrated circuit (few transistors)

Jack Kilby, TI - 1958 - Nobel prize (2000)

Dimension: 11 × 1.6 mm<sup>2</sup>

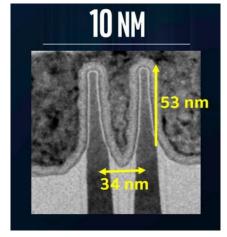

Intel 10 nm process node

National technology roadmap for semiconductors (NTRS)

Now ITRS (I: international)

Y. He et al., Nature **571**, 371 (2019)

> 230 citations

### *p-n* junction

# **Some applications**

- Bipolar transistors

- LEDs

- Laser diodes

- Solar cells

- Photodetectors

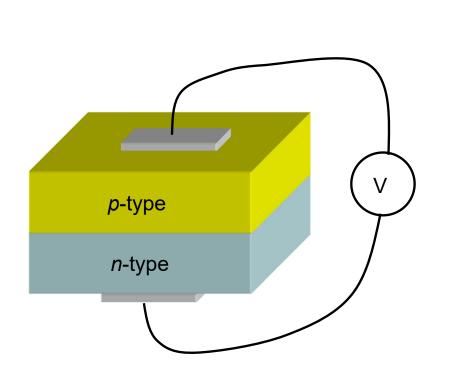

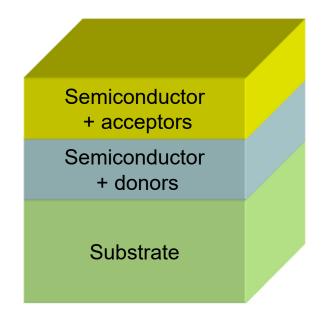

### *p-n* junction (2D-geometry)

#### Made of two adjacent semiconductor layers which are p-type and n-type doped

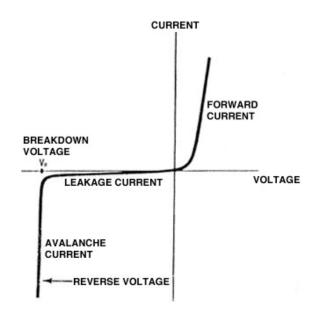

A p-n junction behaves like a diode (rectifying behavior)

Early historical account detailed in: W. Shockley, Bell Syst. Tech. J. **28**, 435 (1949); C.-T. Sah, R. N. Noyce, and W. Shockley, Proc. IRE **45**, 1228 (1957) > 1600 citations

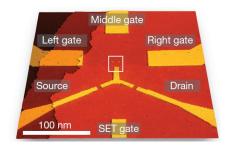

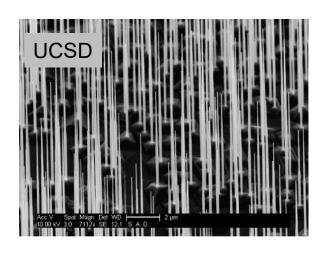

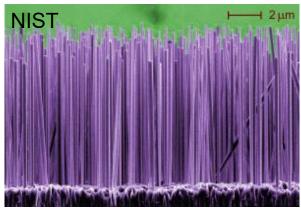

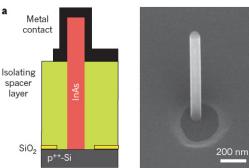

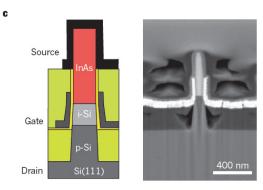

### *p-n* junction (research, nanowire geometry)

#### **Semiconductor nanowires (candidates for tunnel-FETs)**

Subthreshold swing < 60 mV/decade at 300 K (cf. forthcoming Lecture 9)

A. M. Ionescu and H. Riel, Nature **479**, 329 (2011) > 2200 citations

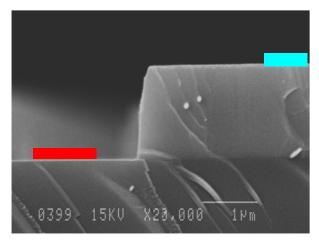

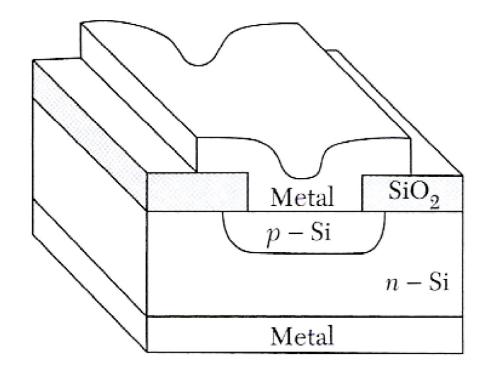

# *p-n* junction fabrication

### **During growth by impurity incorporation**

SEM image of a *p-n* junction (LED)

# *p-n* junction fabrication

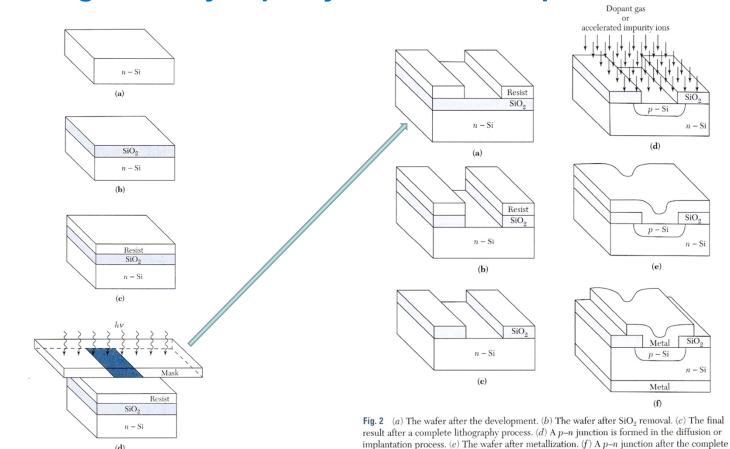

#### Post-growth: by impurity diffusion or implantation

# *p-n* junction fabrication

#### Post-growth: by impurity diffusion or implantation

processes.

Fig. 1 (a) A bare n-type Si wafer. (b) An oxidized Si wafer by dry or wet oxidation. (c) Application of resist. (d) Resist exposure through the mask.

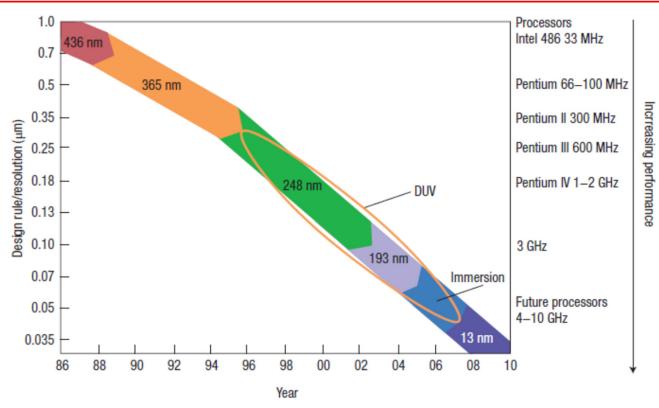

### **Optical lithography**

Speed/power tradeoff ⇒ CPU underclocking can save a lot of power while sacrificing much less the performance (motivation for multicore CPUs)

**Example:** Intel chips (2008), single core underclocking by 20% will save half the power for 13% less performance!

### Optical lithography

The fabrication of integrated circuits (ICs) relies on expensive photolithography systems

Patterns optically imaged onto Si wafers covered with a photoresist

- Leading company: ASML (Dutch), >3/4 of the market ⇒ provider of immersion and EUV lithography machines (sole supplier of EUV tools, market capitalization in 2024 ~US\$400 billion)

- Other players: Canon, Nikon, Ultratech (now part of Veeco Instr.) (USA)

Optical lithography machines set the transistor technology node, i.e., the typical halfpitch (≡ half distance between identical features in an array) for a memory cell. 22 nm technology node for the CMOS process, e.g., multicore processors. 14 nm technology node introduced by Intel at the end of 2014 (broad OEM, 2015)

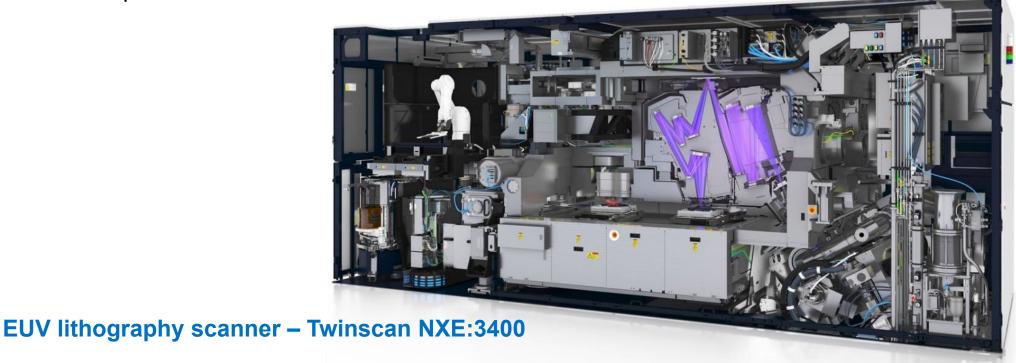

### **Optical lithography**

#### **New generation of wafer stepper:**

- Lens-free optical lithography

- All-mirror-based technology operating in the extreme UV (13.5 nm), hence under vacuum (to avoid air absorption)

- Used by Intel, IBM, Samsung and TSMC

- Cost up to 200 M\$/unit for the Twinscan NXE:3600D

# *p-n* junction: how does it work?

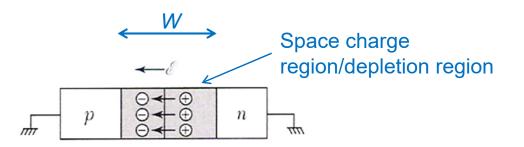

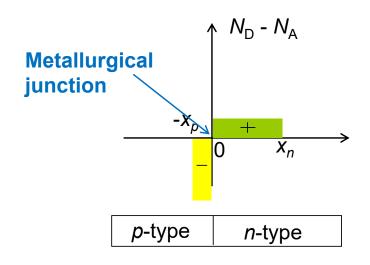

Case of the abrupt *p-n* junction (metallurgical junction)

At thermal equilibrium

$$E_{\mathsf{F}}$$

$E_{\mathsf{V}}$   $E_{\mathsf{V}}$

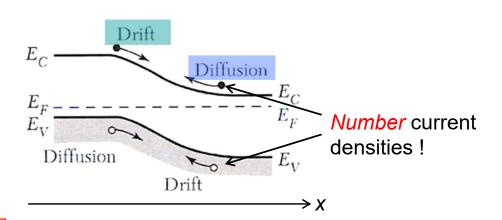

- Concentration gradients ⇒ diffusion currents

- Uncompensated ionized impurities ⇒ built-in electric field ⇒ drift currents

### *p-n* junction at equilibrium

Diffusion and drift currents

$$J_{n,drift} = \sigma_n \mathbf{E} = e \mu_n n \mathbf{E}$$

$$J_{n,diff} = eD_n \operatorname{grad} n$$

#### **Einstein relation:**

$$\frac{D}{\mu} = \frac{k_{\rm B}T}{e}$$

Diffusion coefficient in cm<sup>2</sup> s<sup>-1</sup>

Link between *number* (*j*) and *electrical* (*J*) current densities:

$$\mathbf{J}_n = -e\mathbf{j}_n$$

and  $\mathbf{J}_p = e\mathbf{j}_p$

#### At thermal equilibrium

The Fermi level is constant throughout the structure (details to be seen in the series)

$$J_n = J_{n,\text{drift}} + J_{n,\text{diff}} = 0$$

(also true for holes)

#### NO "net" current flowing through the junction

To be verified in the exercises

$$J_{n} = e \mu_{n} nE + eD_{n} \frac{dn}{dx} = \mu_{n} n \frac{dE_{F}}{dx} = 0$$

Keep in mind that Ohm's law is valid provided  $v_{\rm d} << v_{\rm th}!$

1D case

Full compensation between the drift and diffusion currents!

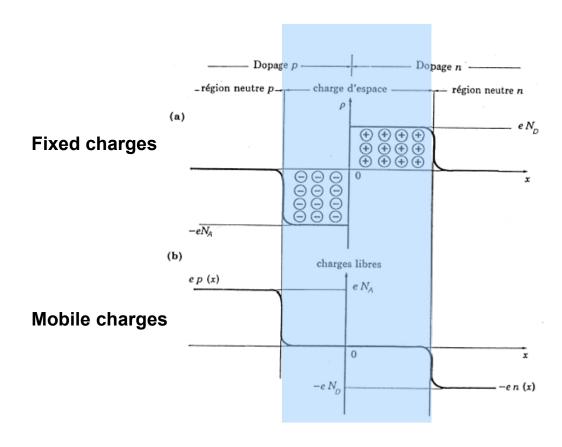

#### **Space charge**

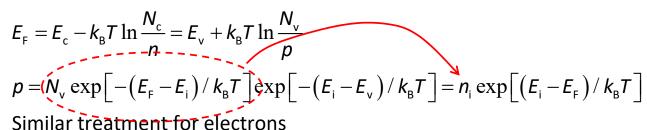

#### At thermal equilibrium

#### **Built-in potential:**

$$eV_{bi} = (E_F - E_i)_n - (E_F - E_i)_p \equiv \text{energy loss across the junction}$$

with

$\frac{E_{\rm F} - E_{\rm i}}{eV_{\rm bi}}$   $\frac{E_{\rm F} - E_{\rm i}}{eV_{\rm bi}}$   $\frac{E_{\rm F}}{E_{\rm i}} E_{\rm F} - E_{\rm i}$   $\frac{E_{\rm F}}{E_{\rm i}} E_{\rm F} - E_{\rm i}$   $(n \approx N_{\rm D} \text{ and } p \approx N_{\rm A})$

If we consider that all impurities are ionized

$$eV_{bi} = E_{g} - k_{B}T \ln \left( \frac{N_{v}N_{c}}{N_{A}N_{D}} \right)$$

Built-in barrier

This built-in potential  $V_{bi}$  is the consequence of the space charge due to carrier diffusion

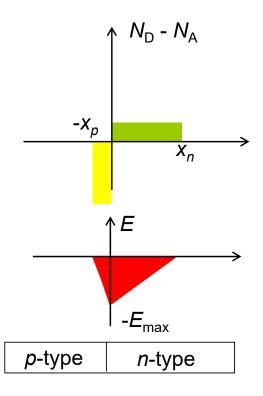

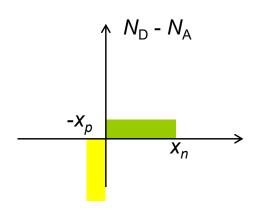

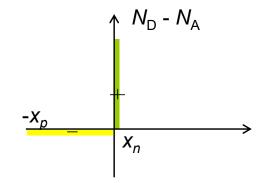

**Abrupt junction** Poisson's equation to be solved as a function of position:

$$\left| \frac{d^2 \phi}{dx^2} = -\frac{\rho(x)}{\varepsilon_r \varepsilon_0} \right|$$

Electrostatic potential vs position

$$\frac{d^2\phi}{dx^2} = e \frac{N_A}{\varepsilon} \quad \text{for} \quad -x_p \le x < 0$$

$$\frac{d^2\phi}{dx^2} = -e \frac{N_D}{\varepsilon} \quad \text{for} \quad 0 < x \le x_n$$

$$\int_{-x_p}^{x_n} \rho dx = 0$$

Charge neutrality:  $x_p N_A = x_n N_D$

**Space charge region extent:**  $W = x_p + x_n$

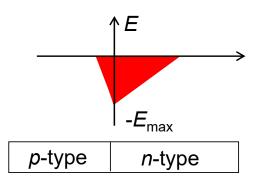

#### Electric field in the space charge region

$$E(x) = -\frac{d\phi}{dx} = -e\frac{N_{A}(x + x_{p})}{\varepsilon} \quad \left[ -x_{p}, 0 \right]$$

$$E(x) = -\frac{d\phi}{dx} = e\frac{N_{D}(x - x_{n})}{\varepsilon} \quad \left[ 0, x_{n} \right]$$

$$|E_{\text{max}}| = e \frac{N_{\text{A}} x_p}{\mathcal{E}} = e \frac{N_{\text{D}} x_n}{\mathcal{E}}$$

#### **Abrupt junction**

$$\begin{aligned} V_{\text{bi}} &= -\int_{-x_p}^{x_n} E(x) dx \\ &= e \frac{N_A}{\varepsilon} \int_{-x_p}^0 (x + x_p) dx - e \frac{N_D}{\varepsilon} \int_0^{x_n} (x - x_n) dx \\ &= e \frac{N_A x_p^2}{2\varepsilon} + e \frac{N_D x_n^2}{2\varepsilon} \\ &= \frac{E_{\text{max}} x_p}{2} + \frac{E_{\text{max}} x_n}{2} = \frac{1}{2} E_{\text{max}} W \end{aligned}$$

Note that:

$$V_{bi} = \frac{1}{\varepsilon} \int_{-x_p}^{x_n} \left[ \int_{-x_p}^{x} \rho dx \right] dx$$

which can also be written:

$$V_{\text{bi}} = \frac{1}{\mathcal{E}} \int_{-x_p}^{x_n} x \rho dx$$

#### **Abrupt junction**

$$V_{bi} = e \frac{N_A X_p^2}{2\varepsilon} + e \frac{N_D X_n^2}{2\varepsilon}$$

Charge neutrality:  $x_p N_A = x_n N_D$

Space charge extent:  $W = x_p + x_n$

$$\Rightarrow W = x_p (1 + N_A/N_D) = x_p (N_D + N_A)/N_D$$

$$W = x_n \dots$$

$$W = \sqrt{\frac{2\varepsilon}{e} \left(\frac{N_{A} + N_{D}}{N_{A} N_{D}}\right) V_{bi}}$$

All the parameters entering into this expression are known beforehand!

**Extent of the space charge region**

#### Example: silicon-based *p-n* junction at 300 K

$$n$$

-type:  $N_{\rm D}$  = 10<sup>18</sup> cm<sup>-3</sup> and  $p = n_{\rm i}^2/N_{\rm D}$  = 10<sup>2</sup> cm<sup>-3</sup> Cf. Lecture 6  $\Rightarrow$  use of mass action law at thermal equilibrium + full ionization of impurities (+ charge  $N_{\rm c}$  = 2.7  $\times$  10<sup>19</sup> cm<sup>-3</sup> and  $N_{\rm v}$  = 1.1  $\times$  10<sup>19</sup> cm<sup>-3</sup> neutrality condition)

We find:

$$eV_{bi} = 0.96 \text{ eV} \qquad eV_{bi} = E_{g} - k_{B}T \ln \left(\frac{N_{v}N_{c}}{N_{A}N_{D}}\right) \qquad \qquad \varepsilon = \varepsilon_{0}\varepsilon_{r}$$

$$\varepsilon_{0} = 8.85 \times 10^{-12} \text{ F m}^{-1}$$

$$W = 50 \text{ nm} \qquad W = \sqrt{\frac{2\varepsilon}{e} \left(\frac{N_{A} + N_{D}}{N_{A}N_{D}}\right)} V_{bi} \qquad \qquad \varepsilon_{r} = 11.9$$

$$e = 1.6 \times 10^{-19} \text{ C}$$

$$E_{\rm max} = 3.8 \times 10^5 \, {\rm V \, cm^{-1}}$$

$E_{\rm max} = 2 V_{\rm bi} \, / \, W$

Other example:  $N_A = N_D = 10^{15} \text{ cm}^{-3}$ ,  $eV_{bi} = 0.61 \text{ eV}$ ,  $W = 1.2 \text{ }\mu\text{m}$

#### Space charge in the *n*-type and *p*-type regions

$$x_n = N_A/(N_D + N_A)W$$

$$x_p = N_D/(N_D + N_A)W$$

If

$$N_D >> N_A$$

then

$$W = \sqrt{\frac{2\varepsilon}{e} \frac{V_{bi}}{N_A}} \quad \text{and } x_p = W$$

One-sided abrupt junction approximation

The space charge mostly extends in the less doped region